巨屌 英特尔代工四大打破性期间看法:为高性能高密度计较铺路

发布日期:2024-12-11 13:35 点击次数:201

在近期举办的IEEE海外电子器件会议IEDM 2024时辰巨屌,英特尔代工(Intel Foundry)展示了四项半导体期间范围的打破以及关联考虑恶果。

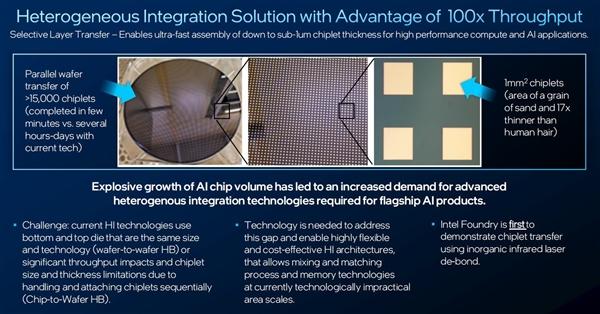

包括:减成法钌互连期间,遴荐性层升沉期间(SLT),环绕栅极硅基RibbonFET CMOS晶体管期间以及用于微缩的2D GAA晶体管的栅氧化层期间。

同期,针对这些前沿期间,英特尔代工提交了七篇关联论文,这些论文涵盖模块化计较系统、GAA 2D FETs栅氧化层模块建造、GaN MOSHEMT晶体管、TMD界面层对pFET性能影响、硅基RibbonFET CMOS晶体管、遴荐性层升沉异构集成期间以及TMD残障与器件性能的关联性考虑。

此外,英特尔还共享了对先进封装和晶体管微缩期间翌日发展的愿景,而且提倡先进内存集成、夹杂键合优化带宽、模块化系统及联结处置决议等调动遵循点,以鼓励AI计较朝着高能效地方发展。

底下咱们浅显先容一下这些半导体代工层面的前沿期间,因为在翌日的半导体产业发展中,这些期间或将慢慢登上舞台,为翌日的半导体行业调动和发展奠定基础。

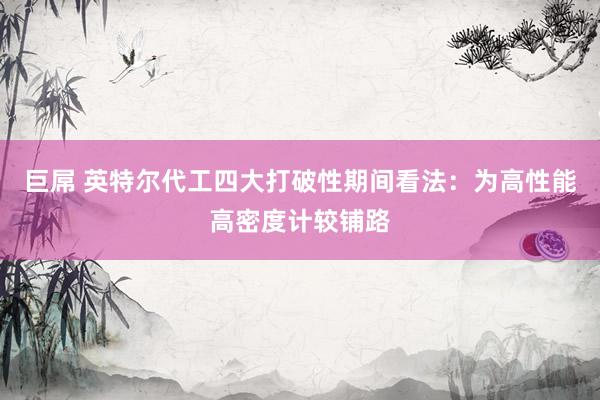

减成法钌互连期间(Subtractive Ruthenium)

该期间是英特尔代工在互连微缩方面的一项紧要卓绝。它依赖于超高纯钌材料,通过特定的工艺纪律,在芯片里面形成互连线,主要作用是不错使芯片盘算已毕更小的互连线隔断,从而优化芯片里面的互邻接构。

不仅如斯,英特尔还应用薄膜电阻率(thin film resistivity)、空气流毒(airgap)期间,使得通孔周围不再需要郁勃的光刻空气流毒。

同期幸免使用遴荐性蚀刻的自瞄准通孔(self-aligned via),当互连间距小于就是25nm时,采纳减成法钌互连期间已毕的空气流毒,不错使线间电容最高裁汰25%,以替代铜嵌入工艺。而线间电容的裁汰有助于普及信号传输速率和裁汰功耗,进而改善合座芯片效率。

减成法钌互连期间一方面带来了更高的功能密度,使得芯片巧合在更小的空间内已毕更复杂的功能。另一方面不错裁汰出产制形本钱,从而促进翌日半导体芯片芯移时间的发展。

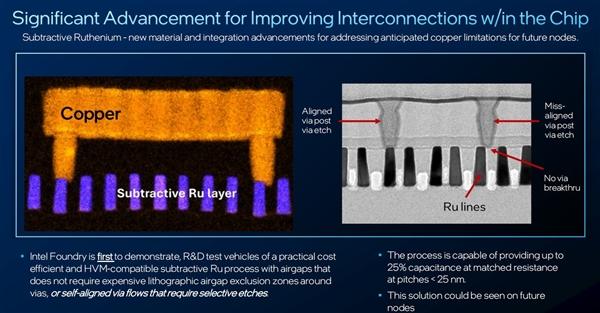

遴荐性层升沉期间(SLT)

该期间主要面向异构集成,它通过高效整合超薄芯粒(chiplet)巨屌,已毕了芯片的功能密度和封装微辞量的显贵普及。